#### **Description**

The SA8345 is one channel H-Bridge driver IC, it provides integrated motor-driver solution for smart hardware, robotics, consumer products and other 12V DC powered or battery-powered motion control applications.

The SA8345 maximum operational voltage is 25.0V. It can supply up to 3.5A of output continuous current and 6.0A of output peak current. There is internal shutdown function for over-temperature protection and over-current protection ( $I_{OCP} = 6.0 \text{ A}$ ).

Package material is Pb-Free Product & RoHS compliant for the purpose of environmental protection and for sustainable development of the earth.

#### **Features**

- Operation voltage up to 25.0V

- Continuous current output up to 3.5A

- Peak current up to 6.0A

- $R_{DSON}$ : 180-m $\Omega$  (HS + LS)

- Support PWM control

- Over current protection

- Over temperature protection

- UVLO protection

- Low standby current

- Low quiescent current

- ESOP8 package

## **Application**

- Robotics (R/C servo, Sweeping robot)

- Smart Hardware

- Relay Driver

- Any relevant DC motor applications.

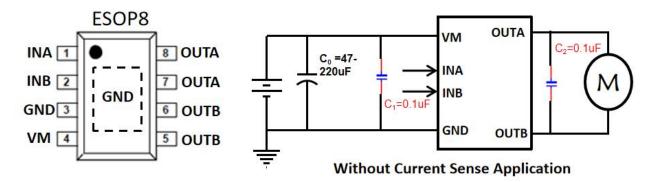

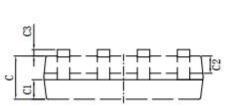

## **SA8345 Package & Simplified Application**

#### **Device Information**

| Part No. | Package | Quantity | Operation Temp. |

|----------|---------|----------|-----------------|

| SA8345   | ESOP8   | 4000     | -40~85 ° C      |

www.szxunrui.cn -1- V2.0

# **Pin Descriptions**

| NO.         | NAME | TYPE | DESCRIPTION                                          |

|-------------|------|------|------------------------------------------------------|

| 1           | INA  | I    | Input INA                                            |

| 2           | INB  | I    | Input INB                                            |

| 3           | GND  | Р    | Ground                                               |

| 4           | VM   | Р    | Power Supply for H-Bridge, Connection 10uF or bigger |

| 4           | VIVI | F    | capacitor between VDD and GND                        |

| 5           | OUTB | 0    | Output OUTB                                          |

| 6           | OUTB | 0    | Output OUTB                                          |

| 7           | OUTA | 0    | Output OUTA, Connection 0.1uF between OUTA and OUTB  |

| 8           | OUTA | 0    | Output OUTA, Connection 0.1uF between OUTA and OUTB  |

| Thermal Pad | GND  | Р    | Connect to GND to improve thermal performance        |

www.szxunrui.cn -2- V2.0

## Absolute Maximum Ratings (T<sub>A</sub>=25°C)

|                    | Parameter                | Min. | Max. | Unit |  |

|--------------------|--------------------------|------|------|------|--|

| Power Supply       | VM                       | -0.3 | 30   | \ \/ |  |

| Input Logic        | INA, INB                 | -0.3 | 7.0  | V    |  |

| ESD(HBM)           | VM, INA, INB, OUTA, OUTB | 2.0  |      | kV   |  |

| Operation temp.    | TJ                       | -40  | 150  | °C   |  |

| Storage temp.      | T <sub>stg</sub>         | -65  | 150  |      |  |

| Thermal resistance | θЈΑ                      |      | 60   | °C/W |  |

## Recommended operating conditions ( $T_A=25^{\circ}C$ )

|                              | Parameter                             | Min. | Max. | Unit |  |

|------------------------------|---------------------------------------|------|------|------|--|

| Power Supply                 | VM                                    | 3.9  | 25.0 | \/   |  |

| Input Logic                  | INA, INB                              | 0    | 5.0  | V    |  |

| Output Contiguous<br>Current | I <sub>OUTA</sub> , I <sub>OUTB</sub> | 0    | 3.5* | А    |  |

Notes: \* Using 25mm<sup>2</sup> FR4 Signal layer PCB (1 oz) under VM=7.2V test.

www.szxunrui.cn - 3 - V2.0

#### **Electrical Characteristics**

$T_A = 25$ °C, over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER UNIT                         | TEST CONDITIONS                             | MIN | TYP  | MAX  | UNIT |  |

|---------------------|----------------------------------------|---------------------------------------------|-----|------|------|------|--|

| POWER S             | SUPPLY (VM)                            |                                             | '   |      |      |      |  |

| VM                  | VM operating voltage                   |                                             | 3.9 |      | 25   | V    |  |

| I <sub>VM_ON</sub>  | VM operating supply current            | VM=12V                                      |     | 1.2  | 2.5  | mA   |  |

| $I_{VM\_OFF}$       | VM sleep current                       | VM=12V                                      |     | 1.0  | 5.0  | uA   |  |

| Ton                 | Turn-on time                           | VM>V <sub>UVLO</sub> , with IN1 or IN2 high |     | 30   | 50   | us   |  |

| MOTOR I             | ORIVER OUTPUTS (OUT1, OUT2)            |                                             |     |      |      | _    |  |

| $R_{\text{DSON}}$   | High-side & Low-side FET on resistance | VM=24V, LS+HS,<br>I <sub>OUT</sub> =1A      |     | 180  |      | mΩ   |  |

| T <sub>DEAD</sub>   | Output dead time                       |                                             |     | 200  |      | ns   |  |

| V <sub>D</sub>      | Body diode forward voltage             | I <sub>OUT</sub> =1A                        |     | 0.8  | 1    | V    |  |

| LOGIC-L             | EVEL INPUTS (INA, INB)                 |                                             |     |      |      | 1    |  |

| V <sub>INH</sub>    | Input logic high voltage               |                                             | 1.5 |      | 5.0  | V    |  |

| V <sub>INL</sub>    | Input logic low voltage                |                                             | 0   |      | 0.5  | V    |  |

| V <sub>IN_HYS</sub> | Input logic hysteresis                 |                                             |     | 0.1  |      | V    |  |

| I <sub>INH</sub>    | Input logic high current               | IN=3.3V                                     |     | 33   | 50   |      |  |

| I <sub>INL</sub>    | Input logic low current                | IN=0V                                       |     | 0    | 1    | uA   |  |

| R <sub>PD</sub>     | Pulldown resistance                    | to GND                                      |     | 100  | 200  | ΚΩ   |  |

| T <sub>PD</sub>     | Propagation delay                      | INx to OUTx change                          |     | 20   |      | ns   |  |

| T <sub>SLP</sub>    | Time to sleep                          | Inputs low to sleep                         |     | 1.0  |      | ms   |  |

| PROTEC              | TION CIRCUITS                          |                                             |     |      |      | •    |  |

| V <sub>UVLO_R</sub> | VM rises until operation recovers      |                                             |     | 3.75 | 3.90 |      |  |

| V <sub>UVLO_F</sub> | VM falls until UVLO triggers           |                                             |     | 3.60 | 3.75 | V    |  |

| V <sub>UVLO_H</sub> | VM undervoltage hysteresis             |                                             |     | 0.15 |      |      |  |

| I <sub>OCP</sub>    | Overcurrent protection trip level      |                                             |     | 7.0  |      | Α    |  |

| T <sub>OCP</sub>    | Overcurrent deglitch time              |                                             |     | 1.5  |      | us   |  |

| T <sub>RETRY</sub>  | Overcurrent retry time                 |                                             |     | 3.0  |      | ms   |  |

| T <sub>SD</sub>     | Thermal shutdown temperature           |                                             |     | 160  |      |      |  |

| T <sub>HYS</sub>    | Thermal shutdown hysteresis            |                                             |     | 30   |      | °C   |  |

www.szxunrui.cn -4- V2.0

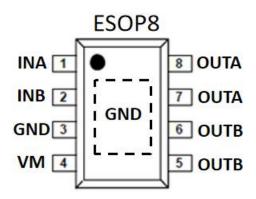

## **Block Diagram**

### **Truth Table**

| INA | INB | OUTA | OUTB | Mode    | Supply Current     |

|-----|-----|------|------|---------|--------------------|

| L   | L   | Hi-Z | Hi-Z | Stop    | $I_{VM\_OFF}$      |

| Н   | L   | Н    | L    | Forward | I <sub>VM_ON</sub> |

| L   | Н   | L    | Н    | Reverse | I <sub>VM_ON</sub> |

| Н   | Н   | L    | L    | Brake   | I <sub>VM_ON</sub> |

www.szxunrui.cn - 5 - V2.0

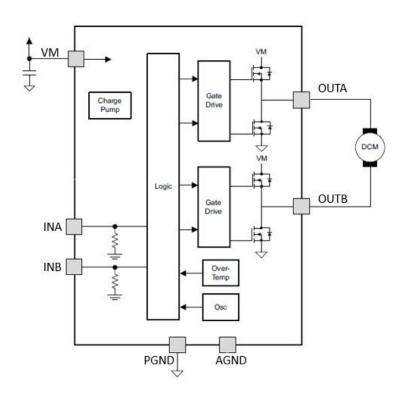

# **Application Notes:**

#### 1. Schematic Descriptions

#### **Notes:**

- 1. This simplified schematic is only as reference in DC motor driver application.

- 2. C0, C1: Power supply VM pin capacitor:

- 1) The capacitor can reduce the power spike when the motor is in motion. To avoid the IC directly damaged by the VM peak voltage. It also can stabilize the power supply voltage and reduce its ripples.

- 2) The C0 capacitor can compensate power when motor starts running.

- 3) The capacitor value determines the stability of the VM during motor in motion. If the large voltage power or a heavy loading motor is used, then a larger capacitor would be needed.

- 4) On the PCB configuration, the C0, C1 must be mounted as close as possible to VM pin .

- 3. C2: The across-motor capacitor

- 1) The C2 capacitors can reduce the power spike of motor in start running. A  $0.1\mu F$  capacitor is recommended.

- 2) The C2 capacitor must be added to the general application.

- 4. RS: The sense resistor in current sense application

- 1) Need to sense output current, the RS is recommended to added between IC GND and PCB ground.

- 2) The C0, C1 negative terminal is recommend connection to IC GND.

www.szxunrui.cn - 6 - V2.0

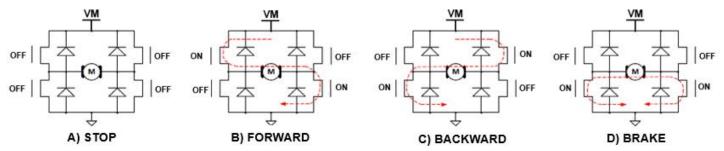

#### 2. Operating Mode Descriptions

H-Bridge basic operating mode:

A) Stop mode

Definition: When INA=INB= L, then OUTA=OUTB=Hi-Z

B) Forward mode

Definition: When INA=H, INB=L, then OUTA=H, OUTB=L

C) Reverse mode

Definition: When INA=L, INB=H, then OUTB=H, OUTA=L

D) Brake mode

Definition: When INA=INB= H, then OUTA=OUTB=L

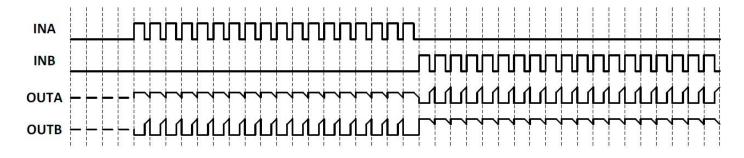

#### E) PWM mode A:

If input INA is PWM signal and INB=0 or if input INB is PWM signal and INA=0, then rotation speed of motor will be controlled by duty cycle of PWM signal. In this mode, motor drive circuit will be switched between switching-on and standby mode. In standby mode, all the power transistors are in off state, the energy stored in motor can only be released slowly from power MOSFET body diode.

Note that rotation speed of motor cannot be precisely controlled by duty cycle of PWM signal as there is a high-impedance state in working mode. If frequency of PWM signal is too high, then the case that motor cannot be started would occur.

Input-Output in PWM mode A

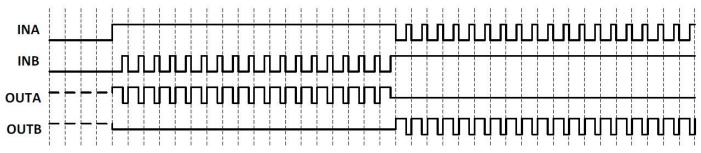

#### F) PWM mode B:

If input INA is PWM signal and INB=1 or if input INB is PWM signal and INA=1, then rotation speed of motor will be controlled by duty cycle of PWM signal. In this mode, motor drive circuit output will be switched between switching-on and brake mode. In brake mode, the energy stored in motor will be released rapidly from low-side NMOS transistor.

Note that rotation speed of motor can be precisely controlled by duty cycle of PWM signal as there is a brake state in working mode and the energy of motor can be released quickly. However, it must be noted that, if frequency of PWM signal is too low, the case that motor cannot be rotated continuously and smoothly due to entering brake mode would occur. To reduce noise of motor, it is recommended that frequency of PWM signal be between 10 KHz and 50 KHz.

Input-Output in PWM mode B

#### 3. Anti-common mode switching-on circuit

In full-bridge drive circuit, the state where both the high-side NMOS power transistor and the low-side NMOS power transistor are switched on at the same time in half bridge is called the common-mode switching-on state. In the common-mode switching-on state there is a power-to-ground, transient, high current, which would cause an extra power loss, and, in extreme cases, would burn the circuit down. With built-in dead time, the common mode switching-on state can be avoided. The typical dead time is 250ns.

#### 4. Thermal protection circuit

If junction temperature of drive circuit exceeds a preset temperature (180°C, typ.), then OTSD circuit starts to work. At this time, control circuit is forced to switch off all output power transistors, and drive circuit output gets into high-impedance state. TSD circuit is designed with thermal hysteresis. Only if junction temperature of drive circuit decrease to a preset temperature (120°C, typ.), can the circuit get back to normal operating condition.

#### 5. Over-current protection (OCP)

While the IC conducts a large current, 6.0A (Typ.), the internal over-current protection function will be triggered. The device enters protection mode of auto-recover to avoid damaging IC and system.

www.szxunrui.cn - 8 - V2.0

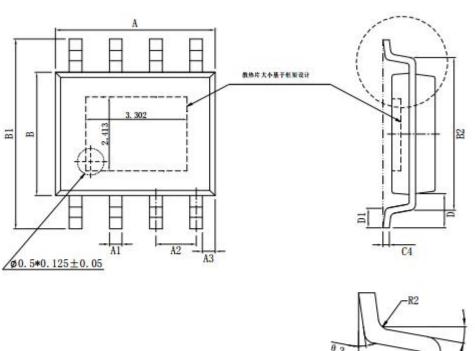

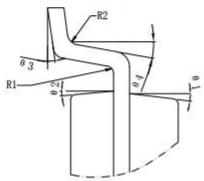

# Package ESOP8

| 注尺寸 | 最小(mm)      | 最大(mm) | 标注  | 最小(mm)      | 最大(mm) |

|-----|-------------|--------|-----|-------------|--------|

| A   | 4. 80       | 5. 00  | СЗ  | 0.00        | 0. 09  |

| A1  | 0.356       | 0. 456 | C4  | 0. 203      | 0. 233 |

| A2  | A2 1. 27TYP |        | D   | 1. 05TYP    |        |

| A3  | 0. 34       | 15TYP  | D1  | 0. 40 0. 80 |        |

| В   | 3. 80       | 4. 00  | R1  | 0. 20TYP    |        |

| B1  | 5. 80       | 6. 20  | R2  | 0. 20TYP    |        |

| B2  | 5. 00TYP    |        | 0 1 | 17° TYP4    |        |

| C   | 1. 30       | 1.60   | θ 2 | 13° TYP4    |        |

| C1  | 0. 55       | 0.65   | θ 3 | 0° ~ 8°     |        |

| C2  | 0. 55       | 0, 65  | 9 4 | 4°          | ~ 12°  |

V2.0 - 9 www.szxunrui.cn